# INGENIERÍA DE COMPUTADORES 3

## Solución al examen de Septiembre 2025

#### PREGUNTA 1 (2 puntos)

Tomando como base el siguiente código VHDL, dibuje el cronograma de evolución de las señales x1, x2, x3, x4 y x5 entre los instantes 0 y 100 ns. Indique el valor inicial de cada una de las señales, así como el instante en que cambian de valor y el nuevo valor.

```

library IEEE;

use IEEE.std_logic_1164.all;

entity cronol is

end entity crono1;

architecture cronol of cronol is

signal s1, x1, x2, x3, x4 : std_logic;

signal x5 : std_logic := '0';

begin

process (s1, x5)

variable temp : std_logic;

begin

temp := x5;

x1 <= s1;

x2 <= x1;

x3 \le temp;

end process;

s1 <= '0', '1' after 10 ns, '0' after 30 ns,

'1' after 40 ns, '0' after 60 ns;

x4 <= transport s1 after 15 ns;

x5 \le s1 after 15 ns;

end architecture cronol;

```

## Solución a la Pregunta 1

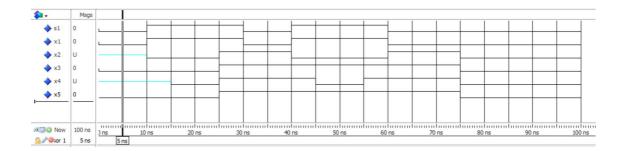

En la siguiente figura se muestra el cronograma de evolución de las señales.

En la siguiente figura se muestra el valor de las señales teniendo en cuenta el retardo delta.

| ps⊸<br>delt | ā− <b></b> | /cronol/sl-/cronol/x5-/<br>/cronol/xl-/<br>/cronol/x2-/<br>/cronol/x3-/<br>/cronol/x4-/ |

|-------------|------------|-----------------------------------------------------------------------------------------|

| 0           | +0         | 0 0000                                                                                  |

| 0           | +1         | 0 0 0 0 0                                                                               |

| 0           | +2         | 0 0 0 0 0                                                                               |

| 10000       | +0         | 10000                                                                                   |

| 10000       | +1         | 11000 0                                                                                 |

| 15000       | +0         | 11000 0                                                                                 |

| 25000       | +0         | 11001 1                                                                                 |

| 25000       | +1         | 11111 1                                                                                 |

| 30000       | +0         | 0 1 1 1 1 1                                                                             |

| 30000       | +1         | 00111 1                                                                                 |

| 40000       | +0         | 10111 1                                                                                 |

| 40000       | +1         | 11011 1                                                                                 |

| 45000       | +0         | 11010 1                                                                                 |

|             | +0         | 11011 1                                                                                 |

|             | +0         | 01011 1                                                                                 |

|             | +1         | 00111 1                                                                                 |

| 75000       | +0         | 00110 0                                                                                 |

| 75000       | +1         | 00000                                                                                   |

#### PREGUNTA 2 (3 puntos)

Diseñe un circuito secuencial síncrono que permita controlar el funcionamiento de una máquina expendedora sencilla. El usuario de la máquina puede introducir únicamente monedas de 5 céntimos y 10 céntimos. Cuando se introducen exactamente 15 céntimos, la máquina expendedora saca un chicle. Este sistema de control debe emitir una señal de apertura (señal abrir) cuando ha detectado que se han introducido 15 céntimos (una moneda de 5 céntimos y una moneda de 10 céntimos, o tres monedas de 5 céntimos). No hace falta que considere el caso en el cual el importe introducido sea superior a 15 céntimos. El sistema de control recibe dos señales de entrada: cinco y diez. La señal cinco es una señal de entrada del circuito que tiene valor '1' durante un tiempo sólo si el usuario introduce una moneda de 5 céntimos. La señal diez es una señal de entrada del circuito que tiene valor '1' durante un tiempo sólo si el usuario introduce una moneda de 10 céntimos.

La **entity** del circuito se muestra a continuación.

El circuito tiene una señal de reloj (clk), dos entradas de un bit (cinco y diez), una señal de reset asíncrona activa en '1' (reset) y una señal de salida de un bit (abrir).

La señal reset es la única señal asíncrona del circuito y pone el circuito en su estado inicial. Este estado inicial indica que no ha recibido ninguna moneda.

La señal abrir se pone a '1' sólo si la máquina ha recibido exactamente 15 céntimos. Esta señal ha de permanece con el valor '1' sólo durante un periodo de la señal de reloj clk.

Escriba en VHDL la **architecture** que describe el comportamiento del circuito en términos de una máquina de Moore. Dibuje el diagrama de estados correspondiente al circuito que ha diseñado.

#### Solución a la Pregunta 2

El Código VHDL 1.1 es una posible solución a la Pregunta 2.

```

1 library IEEE;

2 use IEEE.std_logic_1164.all;

4 entity maquina is

: out std_logic;

port( abrir

5

: in std logic;

cinco

6

diez : in std_logic;

reset : in std_logic;

clk : in std_logic);

9

10 end entity maquina;

12 architecture fsm of maquina is

signal internal_state: std_logic_vector (1 downto 0);

15 --Cálculo del próximo estado

proximo_estado: process (clk, reset)

17 begin

if (reset = '1') then

18

internal state <= "00";</pre>

19

elsif (rising_edge(clk)) then

20

case internal_state is

21

when "00" =>

22

if cinco= '1' then

internal_state <= "01";</pre>

elsif diez = '1' then

internal_state <= "10";</pre>

26

end if;

27

when "01" =>

28

if cinco = '1' then

29

internal_state <= "10";</pre>

30

elsif diez = '1' then

31

internal_state <= "11";</pre>

end if;

when "10" =>

if cinco = '1' then

internal_state <="11";</pre>

36

end if;

37

when others=>

38

internal_state <= "00";</pre>

39

end case;

40

end if;

41

end process proximo_estado;

salida: process (internal_state)

43

begin

44

abrir <= '0';

if internal_state = "11" then

abrir <= '1';

47

end if;

48

end process salida;

49

51 end architecture fsm;

```

Código VHDL 1.1: Máquina expendedora.

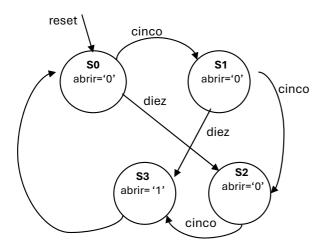

En la siguiente figura se muestra el diagrama de estados del circuito, que tiene cuatro estados (S0, S1, S2 y S3). El estado S0 es el inicial, donde aún no se ha recibido ninguna moneda, en el estado S1 se han recibido 5 céntimos, en el estado S2 se han recibido 10 céntimos y en el estado S3 se han recibido los 15 céntimos.

#### PREGUNTA 3 (2 puntos)

Escriba en VHDL la **architecture** que describe el comportamiento de un circuito combinacional que tiene como señal de salida el número de ceros que contiene la señal de entrada de izquierda a derecha hasta que se encuentra el primer uno. La **entity** del circuito se muestra a continuación.

```

entity numCeros is

port( Y : out std_logic_vector(3 downto 0);

X : in std_logic_vector(7 downto 0) );

end entity numCeros;

```

El circuito tiene una señal de entrada de ocho bits (X) y una señal de salida de cuatro bits (Y).

La señal Y indica en binario sin signo el número de bits que tiene la entrada X con valor '0' hasta que se encuentra el primer bit con valor '1', empezando a revisar los bits de la señal X de izquierda a derecha. Por ejemplo, cuando la señal X tiene el valor "00100101", la señal Y tiene el valor "0010" que se corresponde con el valor decimal 2.

#### Solución a la Pregunta 3

El código VHDL 1.2 describe el comportamiento del circuito.

```

1 library IEEE;

use IEEE.std_logic_1164.all;

3 use IEEE.numeric_std.all;

4 architecture numCeros of numCeros is

process (x)

6

variable count: unsigned (3 downto 0);

begin

count := "0000";

9

for i in 7 downto 0 loop

10

case x(i) is

11

when '0' => count := count + 1;

12

when others => exit;

end case;

14

end loop;

15

y <= std_logic_vector(count);

16

end process;

17

18 end numCeros;

```

Código VHDL 1.2: Circuito detector.

### PREGUNTA 4 (3 puntos)

Programe en VHDL un banco de pruebas que compruebe, para todos los posibles valores de la señal de entrada, si el circuito que ha diseñado al contestar a la Pregunta 3 se comporta correctamente.

Explique detalladamente cómo el programa de test comprueba exhaustivamente el valor del UUT para todos los posibles valores de la entrada.

El banco de pruebas debe comprobar que los valores obtenidos del UUT coinciden con los esperados, mostrando el correspondiente mensaje en caso de que no coincidan. Al final del test, debe mostrarse un mensaje indicando el número total de errores.

#### Solución a la Pregunta 4

El Código VHDL 1.3 es el diseño del banco de pruebas solución de la Pregunta 4.

```

1 library IEEE;

use IEEE.std_logic_1164.all;

3 use IEEE.numeric std.all;

4 entity bp_circ is

5 end entity bp_circ;

6 architecture bp_circ of bp_circ is

signal y : std_logic_vector(3 downto 0); -- Conectar salida UUT

signal x : std_logic_vector(7 downto 0); -- Conectar entrada UUT

component numCeros is port

( y : out std_logic_vector(3 downto 0);

x : in std_logic_vector(7 downto 0));

end component numCeros;

12

13 begin

-- Instanciar y conectar UUT

14

uut : component numCeros port map( y=> y, x => x);

15

16

gen_vec_test : process

variable test_in : unsigned (7 downto 0); -- Vector de test

17

variable y2: std_logic_vector(3 downto 0);

18

variable num_errores: integer:=0;

begin

20

test_in := B"00000000";

21

for count in 0 to 2**8-1 loop

22

x <= std_logic_vector(test_in);</pre>

wait for 10 ns;

if std match (x,"00000000") then y2 := "1000";

25

elsif std_match(x,"00000001") then y2 := "0111";

elsif std_match(x,"0000001-") then y2 := "0110";

27

elsif std_match(x,"000001--") then y2 := "0101";

elsif std_match(x,"00001---") then y2 := "0100"; elsif std_match(x,"0001----") then y2 := "0011";

29

30

elsif std_match(x, "001----") then y2 := "0010";

31

elsif std_match(x,"01-----") then y2 := "0001";

else y2 := "0000";

33

end if;

34

test_in := test_in + 1;

35

assert(y2 = y)

36

report "ERROR. La salida del circuito no corresponde con la

37

salida esperada";

if (y2/=y) then num_errores := num_errores+1;

38

end if;

39

end loop;

41

report "Hay " & integer'image(num_errores) & " errores.";

42

end process gen_vec_test;

44 end architecture bp_circ;

```

Código VHDL 1.3: Banco de pruebas.